Refereed Journal Papers Published:

- M.H. Cheng, A.J. Chicco, D. Ball, and T. W. Chen, “Analysis of Mitochondrial Oxygen Consumption and Hydrogen Peroxide Release from Cardiac Mitochondria Using Electrochemical Multi-Sensors”, Sensors and Actuators B: Chemical, 2022. https://doi.org/10.1016/j.snb.2022.131641.

- G.D. Catandi, L.C. LiPuma, Y.M. Obeidat, L.J. Maclellan, C.D. Broeckling, T. Chen, A.J. Chicco, and E.M. Carnevale. “Oocyte metabolic function, lipid composition, and developmental potential are altered by diet in older mares.” Reproduction 2022, Vol. 163, Issue 4. https://doi.org/10.1530/REP-21-0351.

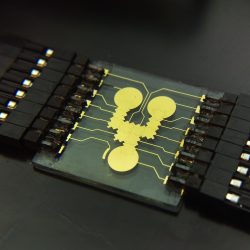

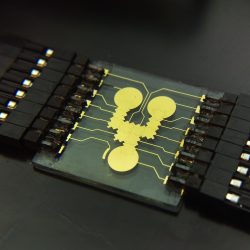

- 1. N. Grant, B. Geiss, A. Demann, S. Field, and T. Chen, (2021) “Design of a Hand-Held and Battery-Operated Digital Microfluidic Device for Lab-on-a-Chip Applications”, Micromachines 2021, 12(9), 1065; https://doi.org/10.3390/mi12091065

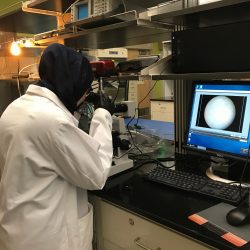

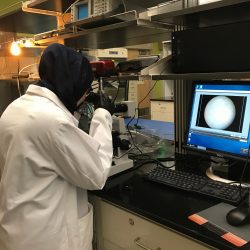

- W. Tedjo, Y. Obeidat, G. Catandi, E. Carnevale, and T. Chen, (2021) “Real-Time Analysis of Oxygen Gradient in Oocyte Respiration Using a High-Density Microelectrode Array”, Biosensors, 2021, 11(8), 256; https://doi.org/10.3390/bios11080256.

- G.D. Catandi, Y. Obeidat, C.D. Broeckling, T. Chen, A.J. Chicco, and E.M. Carnevale, (2021). “Equine Maternal Aging Affects Oocyte Lipid Content, Metabolic Function and Developmental Potential”, Reproduction 2021 Vol. 161, issue 4. https://doi.org/10.1530/REP-20-0494

- C. Begly, D. Ackart, J. Mylius, R. Basaraba, A. J. Chicco, and T. Chen, (2020) “Study of Real-Time Spatial and Temporal Behavior of Bacterial Biofilms Using 2D Impedance Spectroscopy”, IEEE Transactions on Biomedical Circuits and Systems, V. 14, No. 5, Oct. 2020. pp. 1051 – 1064, DOI: 10.1109/TBCAS.2020.3011918.

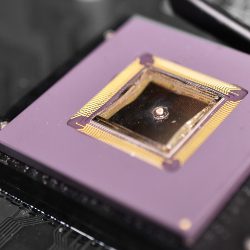

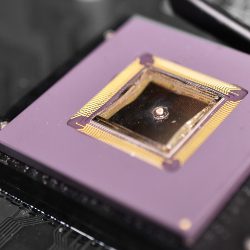

- W. Tedjo and T. Chen, (2019) “An Integrated Biosensor System with a High-Density Microelectrode Array for Real-Time Electrochemical Imaging”, IEEE Trans. on Biomedical Circuits and Systems. Vol. 14, No. 1, Feb. 2020. pp. 20 – 35. doi: 10.1109/TB-CAS.2019.2953579.

- Di Donato Catandi, G., Obeidat, Y., Chicco, A. J., Chen, T. W., Carnevale, E. (2019). “Basal and maximal oxygen consumption of oocytes from young and old mares” (vol. 31). Reproduction, Fertility and Development. DOI: 10.1071/RDv31n1Ab167

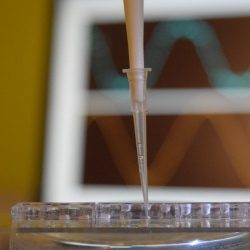

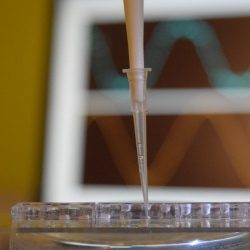

- Y. Obeidat, M. H. Cheng, G. Catandi, E. Carnevale, A. Chicco, and T. Chen, (2019) “Design of a multi-sensor platform for integrating extracellular acidification rate with multi-metabolite flux measurement for small biological samples”, Biosensors and Bioelectronics, Vol. 133, pp. 39 – 47, 2019, https://doi.org/10.1016/j.bios.2019.02.069

- Y. Obeidat, G. Catandi, E. Carnevale, A. Chicco, A. DeMann, S. Field, and T. Chen, (2019) “A Multi-Sensor System for Measuring Bovine Embryo Metabolism”, Biosensors and Bioelectronics, Elsvier, Vol.126 1 (2019) 615 – 623,

https://doi.org/10.1016/j.bios.2018.09.071 - Y. Obeidat, A. Evans, W. Tedjo, A. Chicco, E. Carnevale, and T. Chen, (2018) “Monitoring Oocyte/Embryo Respiration Using Electrochemical-Based Oxygen Sensors”, Sensors & Actuators B. Chemical, Elsvier, 276 – 281, 2018. https://doi.org/10.1016/j.snb.2010.

- W. Tedjo, J. Nejad, R. Feeny, L. Yang, C. Henry, T. Stuart, and T. Chen, (2018) “Electrochemical Biosensor System Using A CMOS Microelectrode Array Provides High Spatially and Temporally Resolved Images”, Biosensors and Bioelectronics, Elsvier, 2018. https://doi.org/10.1016/j.bios.2018.04.009.

- A. A. Maciejewski, T. Chen, Z. S. Byrne, M. A. De Miranda, L. B. Sample Mcmeeking, B. M. Notaros, A. Pezeshki, S. Roy, A. M. Leland, M. D. Reese, A. H. Rosales, T. J. Siller. R. F. Toftness, and O. Notaros, (2017) “A Holistic Approach to Transforming Undergraduate Electrical Engineering Education”, IEEE Access, Vol. 5, No. 1, DECEMBER 2017. DOI: 10.1109/ACCESS.2017.2690221

- L. Wang, L. Yang, M. Veselinovic, L. Yang, B. Geiss, D.S. Dandy, and T. Chen, (2016) “A Sensitive DNA Capacitive Biosensor Using Interdigitated Electrode”, Biosensors and Bioelectronics, Elsevier, http://dx.doi.org/10.1016/j.bios.2016.09.006, 2016.

- M. Hossein, J. Badar, J. DiLulli, and T. Chen, (2016) “A Practical Automated Timing and Physical Design Implementation Methodology for the Synchronous Asynchronous Interface and Multi-Voltage Domain in High Speed Synthesis”, Microprocessors and Microsystems, Elsevier, Volume 45, Part B, pp. 241 – 252, September,

2016, https://doi.org/10.1016/j.micpro.2016.05.012. - Y. Statter and T. Chen, (2016) “Gamma: A SaaS-Enabled Fast and Accurate Analog Design System”, Integration, the VLSI Journal, Elsevier, Volume 55, pp. 67 – 84, September, 2016, https://doi.org/10.1016/j.vlsi.2016.03.003.

- Y. Statter and T. Chen, (2016) “A Novel High-Throughput Method for Table Look-Up Based Analog Design Automation”, Integration, the VLSI Journal, Elsevier, Volume 52, pp. 168 – 181, January 2016, https://doi.org/10.1016/j.vlsi.2015.09.003

- J. B. Wydallis, R. M. Feeny, W. Wilson, T. Kern, T. Chen, S. Tobet, M. Reynolds, and C. Henry, (2015) “Spatiotemporal Norepinephrine Mapping Using a High-Density CMOS Microelectrode Array”, Lab on a Chip, Royal Society of Chemistry, Oct. 2015. DOI: 10.1039/c5lc00778j

- R. M. Feeny, J. B. Wydallis, T. Chen, S. Tobet, M. Reynolds, and Charles S. Henry, (2015) “Analysis of Nitric Oxide from Chemical Donors Using CMOS Platinum Microelectrodes”, Electroanalysis, Feb. 2015. DOI:10.1002/elan.201400510

- M. Hossain, C. Desai, T. Chen, V. Agarwal, (2015) “Synthesis-Based Design and Implementation Methodology of High-Speed, High-Performing Unit: L2 Cache Unit Design”, Integration: The VLSI Journal, vol 49, pp. 125 -136, March 2015, https://doi.org/10.1016/j.vlsi.2014.10.001.

- R. Selby and T. Chen, (2013) “A 2nd Order CMOS Sigma-Delta Modulator Design Suitable for Low-Power Biosensor Applications”. Springer series “Communications in Computer and Information Science” (CCIS) Biomedical Engineering Systems and Technologies, pp 3 – 12, Springer-Verlag, Dec. 2013. doi: 10.1007978-3-662-44485-6

- P. Hernandez, M. de Miranda, and T. Chen, (2013) “Connecting the STEM Dots: Measuring the Effect of an Integrated Engineering Design Intervention”, International Journal of Technology and Design Education. doi: 10.1007s10798-013-9241-0, 2013.

- W. Pettine, M. Jibson, T. Chen, S. Tobet, C. Henry, (2012) “Charaterization of novel microelectrode geometries for detection of neurotransmitters”, IEEE Sensors Journal, Vol. 12, No. 5, May, 2012, DOI: 10.1109/JSEN.2011.2163708.

- C. Thangaraj, C. Alkan, T. Chen, (2010) “Rapid Design Space Exploration Using Legacy Design Data And Technology Scaling Trend Integration”, The VLSI Journal, Vol. 43, Issue 2, April, 2010, https://doi.org/10.1016/j.vlsi.2009.11.002.

- C. Thangaraj, R. Pownall, G. Yuanb, P. Nikkel, K. Kear, and T. Chen, (2010) “Fully CMOS-Compatible On-Chip Optical Clock Distribution and Recovery”, IEEE Trans. on VLSI Systems, Vol. 18, No. 10, 2010, DOI: 10.1109/TVLSI.2009.2024206.

- R. Pownall, C. Thangaraj, G. Yuanb, P. Nikkel, T. Chen, and K. Lear, (2009) “CMOS optoelectronic components for clock distribution”, Microelectronic Engineering, Vol. 87, pp. 1838 – 1845, 2010, https://doi.org/10.1016/j.mee.2009.10.051.

- J. Gregg and T. Chen, (2007) “Post Silicon Power/Performance Optimization in the Presence of Process Variations Using IndividualWell Adaptive Body Biasing (IWABB),” IEEE Trans. on VLSI Systems, Vol. 15, No. 3, pp. 366 – 376, March, 2007, DOI: 10.1109/TVLSI.2007.893626.

- R. Pownall, G. Yuan, T.W. Chen, P. Nikkel, and K.L. Lear, (2007) “Geometry Dependence of CMOS Compatible, Polysilicon, Leaky-Mode Photodetectors”, IEEE Photonics Technology Letters, Vol. 19, No. 7, 2007, DOI: 10.1109/LPT.2007.893573.

- G. Yuan, R. Pownall, P. Nikkel, C. Thangaraj, T.W. Chen, and K.L. Lear, (2006) “Characterization of CMOS compatible, waveguide coupled leaky-mode photodetectors”, IEEE Photonics Technology Letters., vol. 18, pp. 1657-1659, August, 2006, DOI: 10.1109/LPT.2006.879527.

- M. Kulkarni and T. Chen, (2005) “A Sensitivity Based Approach to Analyzing Signal Delay Uncertainty of Coupled Interconects”, IEEE Trans. on Computer-Aided Design of Integrated Circuits and Systems, Vol. 24, No. 9, pp. 1336 – 1346, Sept. 2005, https://doi.org/10.1109/TCAD.2005.852059.

- T. Chen, (2005) “On the Impact of On-Chip Inductance on Signal Nets Under the In uence of Power Grid Noise,” IEEE Trans. on VLSI Systems, Vol.13, No.3, pp. 339 – 348, March, 2005, DOI: 10.1109/TVLSI.2004.842893.

- G. Cho and T. Chen, (2005) “Comparative Assessment of Adaptive Body-Bias SOI Pass-Transistor Logic,” An International Journal of Analog Integrated Circuits and Signal Processing, Kluwer Publications. Vol.42, pp. 219 – 229, March, 2005, https://doi.org/10.1007/s10470-005-6756-7.

- T. Chen and A. Hajjar, (2004) “Statistical Timing Analysis of Coupled Interconnects Using Quadratic Delay Change Characteristics”, IEEE Trans. on Computer-Aided Design of Integrated Circuits and Systems, Vol. 23, No. 12, pp. 1677 – 1683, December 2004, https://doi.org/10.1109/TCAD.2004.837720.

- G. Esch Jr. and T. Chen, (2004) “A Near Linear CMOS IO Driver with Less Sensitivity to Process, Voltage, and Temperature Variations,” IEEE Trans. on VLSI Systems. pp. 1253 – 1257, Vol. 12, No. 11, November 2004, DOI: 10.1109/TVLSI.2004.836321.

- G. Cho and T. Chen,(2004) “Synthesis of Single/Dual-Rail Mixed PTL/Static Logic for Low-Power Applications,” IEEE Trans. on Computer-Aided Design of Integrated Circuits and Systems, Vol. 22, No. 2, pp. 229 – 242, February 2004, DOI: 10.1109/TCAD.2003.822121.

- T. Chen and S. Naffziger, (2003) “Comparison of Adaptive Body Bias(ABB) And Adaptive Supply Voltage (ASV) For Improving Delay and Leakage Under the Presence of Process Variation,” IEEE Trans. on VLSI Systems, Vol. 11, No. 5, pp. 888 – 899, October 2003, DOI: 10.1109/TVLSI.2003.817120.

- J. Kim and T. Chen, (2003) “Combining Static and Dynamic Features Using Neural Networks and Edge Fusion for Video Object Extraction,” IEE Proceedings-Vision, Image, and Signal Processing, Vol. 150, No. 3, pp. 160 – 167, June 2003, DOI: 10.1049/ip-vis:20030361.

- J. Kim and T. Chen, (2003) “A VLSI Architecture for Video-Object Segmentation,” IEEE Trans. on Circuits and Systems for Video Technology (CSVT), Vol. 13, No. 1, pp. 83 – 96, January 2003, DOI: 10.1109/TCSVT.2002.808082.

- T. Chen, A. Bai, A. Hajjar, A. von Mayrhauser, and C. Anderson, (2002) “Fast Antirandom (FAR) Test Generation to Improve the Quality of Behavioral Model Verification,” Journal of Electronic Testing: Theory and Applications (JETTA), Kluwer Academic Publishing, Vol. 18, No. 6, pp. 583 – 594, December 2002, https://doi.org/10.1023/A:1020844805564.

- J. Kim and T. Chen, (2001) “Multiple Feature Clustering for Image Sequence Segmentation,” Pattern Recognition Letters, Elsvier Science B.V., Vol. 22, pp. 1207 – 1217, July 2001, https://doi.org/10.1016/S0167-8655(01)00053-8.

- G. Cho and T. Chen, (2001) “On Mixed PTL/Static Logic for Low-Power and High-Speed Circuits,” VLSI Design: In International Journal of Custom-Chip Design, Simulation and Testing, Vol. 12, No. 3, pp. 399 – 406, July 2001, https://doi.org/10.1155/2001/59548.

- F. Alzaharani and T. Chen, (2000) “On-Chip TEC-QED Code for Ultra-Large, Single-Chip Memory Systems,” International Journal of Computers and Electrical Engineering, Vol. 26, No. 6, pp. 317 – 335, December 2000, https://doi.org/10.1016/S0045-7906(99)00034-8.

- V.K. Kim and T. Chen, (1999) “On Comparing Functional Fault Coverage and Defect Coverage for Memory Testing,” IEEE Trans. on Computer-Aided Design of Integrated Circuits and Systems, Vol. 18, No. 11, pp. 1672 – 1683, November 1999, DOI:10.1109/43.806812.

- Y.B. Kim and T. Chen, (1999) “Assessing Merged DRAM/Logic Technology,” Integration: The VLSI Journal, Elsevier Science, Vol. 27, No. 2, pp. 179 – 194, September 1999, https://doi.org/10.1016/S0167-9260(99)00006-1.

- T. Chen, V.K. Kim, and M. Tegethoff, (1999) “IC Manufacturing Test Cost Estimation at Early Stages of the Design Cycle,” Microelectronics Journal, Elsevier Science, Vol. 30, No. 8, pp. 733 – 738, August 1999, https://doi.org/10.1016/S0026-2692(98)00159-1.

- T. Chen, V.K. Kim, and M. Tegethoff, (1999) “IC Yield Estimation at Early Stages of the Design Cycle,” Microelectronics Journal, Elsevier Science, Vol. 30, No. 8, pp. 725 – 732, August 1999, https://doi.org/10.1016/S0026-2692(98)00158-X.

- G. Sunada, T. Chen, and J. Jin (1999) “COBRA: a 100 MOPS Single-Chip Programmable and Expandable FFT,” IEEE Trans. on VLSI Systems, Vol. 7, No. 2, pp. 174 – 182, June 1999, DOI: 10.1109/92.766744.

- A. Hajjar and T. Chen, (1999) “A VLSI Architecture for Real-Time Edge Linking,” IEEE Trans. on Pattern Analysis and Machine Intelligence, Vol. 21, No. 1, pp. 89 – 94, January 1999, https://doi.org/10.1007/978-0-387-35311-1 2.

- M. Schaffer and T. Chen, (1998) “A Tree Matching Algorithm and VLSI Architecture for Real-Time 2D Object Classification” Journal Real-Time Imaging ,” Elsevier Science Publisher, Academic Press, Vol. 4, No. 3, pp. 193 – 202, June 1998, https://doi.org/10.1006/rtim.1997.0095.

- M. Tegethoff and T. Chen, (1997) “Simulation Techniques for the Manufacturing Test of Boards and MCMs,” Journal of Electronic Testing: Theory and Applications (JETTA), Kluwer Academic Publishing, Vol. 10, No. 1/2, pp. 137 – 149, February 1997, https://doi.org/10.1007/978-1-4615-6107-1 13.

- F. Alzahrani and T. Chen, (1997) “A Real-Time Edge Detector: Algorithm and VLSI Architecture” Journal of Real Time Imaging, special issue on \Special-Purpose Architectures for Real-Time Imaging,” Elsevier Science Publisher, Vol. 3, No. 5, pp.363 – 378, November 1997, https://doi.org/10.1006/rtim.1996.0071.

- M. Tegethoff and T. Chen, (1996) “Sensitivity Analysis of Critical Parameters in Board Test,” IEEE Design & Test of Computers, Vol. 13, No. 1, pp. 58{63, January 1996, DOI: 10.1109/TTE.2021.3050987.

- M. Tegethoff and T. Chen, (1995) “A Clustered Yield Model for SMT Boards and MCMs,” IEEE Trans. on Components, Packaging, and Manufacturing Technology, Part B: Advanced Packaging, Vol. 18, No. 4, pp. 640 – 643, November 1995, DOI: 10.1109/96.475269.

- X. Wang and T. Chen, (1995) “Performance and Area Optimization of VLSI Systems Using Genetic Algorithms.” VLSI Design: An International Journal of Custom-Chip Design, Simulation and Testing, Vol. 3, No. 1, pp. 43 – 51, January 1995, https://doi.org/10.1155/1995/26912.

- T. Chen and L. Zhu, (1993) “An Expandable Column FFT Architecture Using Circuit Switching Networks,” The Journal of VLSI Signal Processing. Vol. 6, No. 5, pp. 243 – 257, May 1993, https://doi.org/10.1007/BF01608537.

- T. Chen and G. Sunada, (1993) “Design of A Self-Testing and Self-Repairing Structure for Highly Hierarchical Ultra-Large Capacity Memory Chips,” IEEE Trans. on VLSI Systems, Vol. 1, No. 2, pp. 88 – 97, June 1993, DOI: 10.1109/92.238427.

- T. Chen, (1993) “From System Design to IC Design in 14 Weeks { Teamwork Makes It Possible,” IEEE Trans. on Education, Vol. 36, No. 1, pp. 137 – 140, February 1993, DOI: 10.1109/13.204833.

Refereed Conference Papers:

- William Tedjo, Rachel Feeny, Chad Eitel, Luke Schwerdtfeger, Stacy Willett, Charles Henry, Stuart Tobet, Tom Chen, “Design of an Integrated Microelectrode Array System for High Spatiotemporal Resolution Chemical Imaging”, IEEE BioCAS, Shanghai, China, Oct. 17 – 19, 2016.

- Lang Yang and Tom Chen, “A Compact Signal Generation and Acquisition Circuit for Electrochemical Impedance Spectroscopy”, IEEE BioCAS, Shanghai, China, Oct. 17-19, 2016.

- Y. Obeidat and T. Chen, “Characterization of an O2 Sensor Using Microelectrodes”, 2016 IEEE SENSORS, Orlando, FL, Oct. 30 – Nov. 2, 2016.

- Abhiram R. Gundla and T. Chen, “A 0.2 nJ/bit QPSK Transmitter with Tuning for Process Variation for Biomedical Telemetry in the MedRadio Band of 401-457MHz”, IEEE 59th Midwest Symposium on Circuits and Systems, Abu Dhabi, United Arab Emirates, 16-19 October 2016.

- Abhiram R. Gundla and T. Chen, ”An Efficient Multi Channel, 425W QPSK Transmitter with Tuning for Process Variation in the Medical Implantable Communications Service (MICS) Band of 4Q2-405MHz”, IFIP/IEEE International Conference on Very Large Scale Integration (VLSI-SoC, Tallin, Estonia, September 26-28, 2016.

- L. Yang and T. Chen, “A Low Power 64-point Bit-Serial FFT Engine for Implantable Biomedical Applications”, 18th Euromicro Conference on Digital System Design (DSD), August. 26-28, Madeira, Portugal, August. 26-28, 2015.

- S. Wright and T. Chen, “A PVT-Compensated Capacitive Sensor with sub-1fF Sensitivity”, IEEE 58th International Midwest Symposium on Circuits and Systems, Fort Collins, CO, August 2-5, 2015.

- A. Reddy Gundla and T. Chen, “A Low Power Frequency Synthesizer for Biosensor Applications in the MedRadio Band”, IEEE 58th International Midwest Symposium on Circuits and Systems, Fort Collins, CO, August 2-5, 2015.

- H. Chi and T. Chen, “CMOS Temperature Sensor with -0.34C to 0.27C Inaccuracy from -30C to 80C”, IEEE Computer Society, Int. Symposium on VLSI, July 9-11, 2014, Tampa, FL.

- T. Kern and T. Chen, “A 0.18m Integrated Impedance Sensor using a Novel Mixed-signal Divider and Automatic Gain Control”, 2014 IEEE Int. Symp. on Circuits and Systems (ISCAS). June 1-4, Melbourne, Australia.

- W. Wilson and T. Chen, “Design of a 50MΩ Transimpedance Amplifier with 0.98fA/Input Inferred Noise in a 0:18µm CMOS Technology”, Proc. of BIODEVICES 2014, Angers, France, March 3-6, 2014.

- S. Tobet, C. Eitel, D. Dandy, R. Bartels, M. Reynolds, T. Chen, and C. Henry, “Slices for Devices: Organotypic slice cultures for in vitro sensor analyses”, 2013 BMES Annual Meeting, Sept. 25-28, Seattle, WA, 2013.

- K. Scholeld and T. Chen, “A Low Power 15-Bit Decimator in 0.18um CMOS for Biomedical Applications”, 16th Euromicro Conference on Digital System Design (DSD), Sept. 4-6, Santander, Spain, 2013.

- R. Quintana, A. Sequra, K. Tucker, and T. Chen, “Design of a Capacitance Sensor in 0.18µm CMOS Technology for Biomedical Application”, IEEE 56th International Midwest Symposium on Circuits and Systems, Aug. 4-7, Columbus, OH, 2013.

- Tucker Kern and Tom Chen, “A Low-Power, Offset-Corrected Potentiostat for Chemical Imaging Applications”, Proc. of LASCAS 2013, Cusco, Peru, Feb. 27-March 1, 2013.

- Ryan Selby, Tucker Kern, William Wilson, and Tom Chen, “A 0.18 µm CMOS Switched Capacitor Amplifier Using Current-Starving Inverter Based Op-Amp for Low-Power Biosensor Application”, Proc. of LASCAS 2013, Cusco, Peru, Feb. 27-March 1, 2013.

- William Wilson, Ryan Selby, and Tom Chen, “A Current-Starved Inverter-Based Differential Amplifier Design for Ultra-Low Power Applications”, Proc. of LASCAS 2013, Cusco, Peru, Feb. 27-March 1, 2013.

- Ryan Selby and Tom Chen. “A 0.18 µm CMOS 2nd Order Sigma-Delta Modulator for Low-power Biosensor Applications”, Proc. of BIODEVICES 2013, Barcelona, Spain, Feb. 11-14, 2013. (Nominated for the Best Paper Award)

- M. Duwe and T. Chen, “Offset Correction of Low Power, High Precision Op Amp Using Digital Assist for Biomedical Applications”, Int. Symp. on Circuits and Systems (ISCAS), p.850-853, Seoul, Korea, May 20 – 23, 2012.

- Kristin Scholeld and Tom Chen, “Low Power Decimator Design Using Bit-Serial Architecture for Biomedical Applications”, 2012 Workshop in the International Multi-Conference of Engineers and Computer Scientists (DATICS-IMECS’12), March 14-16, 2012, Hong Kong, China.

- M. Duwe, T. Chen, “Low power integrated potentiostat design for electrodes with improved accuracy”, Midwest Symposium on Circuits and Systems (MWSCAS), Seoul, Korea, August, 2011

- C. Jena, T. Mason, and Tom Chen, “On Power & Performance Tradeoff of L2 Cache Compression”, 2010 IEEE APCCAS. Kuala Lumpur, Malaysia, Dec. 6-9, 2010.

- Z. Cashero, A. Chen, R. Hoppal, T. Chen, “Fast Evaluation of Analog Circuits Using Linear Programming”, 2010 IEEE Computer Society Annual Symposium on VLSI, Lixouri, Kefalonia, Greece, July 5-7, 2010.

- A. Chen, R. Hoppal, and T. Chen, “On CMOS Memory Design In Low Supply Voltage For Integrated Biosensor Applications”, 2010 13th Euromicro Conference on Digital System Design: Architectures, Methods and Tools. Lille, France, Sept. 1-3, 2010.

- T. Wu, C. Alkan, and T. Chen, “Complexity Reduction for Analog Circuit Performance Models Using Random Forests”, 17th IFIP/IEEE Int. Conf. on VLSI, Florianopolis, Brazil, Oct. 12 – 14, 2009.

- T. Wu, C. Alkan, and T. Chen, “Analysis and Improvement of SER Immunity of Combinational Logic”, 16th IFIP/IEEE Int. Conf. on VLSI (VLSI-SOC 2008), Rhodes Island, Greece, Oct. 13 – 15, 2008.

- C. Thangaraj, T. Chen, “A Fully CMOS-Compatible Optical H-Tree & Clock Recovery System”, 16th IFIP/IEEE Int. Conf. on VLSI (VLSI-SOC 2008), Rhodes Island, Greece, Oct. 13 – 15, 2008.

- T. Wu, A. Cengiz, T. Chen, “Improving SER Immunity of Combinational Logic Using Combinations of Spatial and Temporal Checking”, 11th Euromicro Conference on Digital System Design, Parma, Italy, 2 – 5 September 2008.

- C. Thangaraj and T. Chen, “Design Target Exploration for Meeting Time-to-Market Using Pareto Analysis”, IEEE International Symposium on Circuits and Systems, Seattle, Washington, USA, 18 – 21 May 2008.

- C. Thangaraj and T. Chen, “Early Design Phase Power Performance Trade-offs Using In-situ Macro Models”, 4th IEEE International Symposium on Electronic Design, Test & Applications, Hong Kong, January 23 – 25, 2008.

- K. L. Lear, G. Yuan, M. D. Stephens, X. He, R. Pownall, R. Yan, P. Nikkel, C. S. Henry, T. W. Chen, and D. S. Dandy, “A Waveguide Biosensors Local Evanescent Field Response to an Immunoassay Comple”, IEEE LEOS Summer Topical Meetings/Biophotonics, paper TuB2.2, Portland, Oregon, July 24, 2007.

- C.V. Tangaraj and T. Chen, “Power and Performance Analysis for Early Design Space Exploration”, Proc. of IEEE Computer Society Symposium on VLSI, Porto Alegre, Brazil, June 9 – 11, 2007.

- C.V. Thangaraj, K. Stephenson, T. Chen, K. Lear, and A.M. Raza, “Design of CMOS Transimpedance Amplifier for On-Chip Waveguide Based Optical Clock Distribution System”, Proc. of SPIE Conference on Mirotechnologies for the New Millennium, Gran Canaria, Spain, May 2 – 4, 2007.

- V. Nawale, T. Chen, “Optimal Useful Clock Skew Scheduling In the Presence of Variations Using Robust ILP-Formulations”, Int. Conf. on Computer-Aided Design (ICCAD), November, 2006.

- R. Pownall, G. Yuan, T. Chen, P. Nikkel, and K.L. Lear, “Geometry Dependence of Leaky-Mode Waveguide-Coupled Polysilicon Photodetector”, LEOS, November, 2006.

- J. Sridharan and T. Chen, “Modeling Multiple Input Switching of CMOS Gates in DSM Technology using HDMR”, Design and Test in Europe (DATE2006), Munich, Germany, March 6-10, 2006.

- C. Alkan and T. Chen, “Routing-Tree Construction with Concurrent Performance, Power and Congestion Optimization”, 2006 IEEE Computer Society Annual Symposium on VLSI, Karlsruhe, Germany, March 2-3, 2006.

- J. Sridharan and T. Chen, “Gate Delay Modeling with Multiple Input Switching for Static (Statistical) Timing Analysis”, 19th International Conference on VLSI Design, Hyderabad, India, January 3 – 7, 2006.

- C. Alkan and T. Chen, “A Progressive Two-Stage Global Routing for Macro-Cell based Designs”, 19th International Conference on VLSI Design, Hyderabad, India, January 3-7, 2006.

- Justin Gregg, Tom Chen, and Katherine McDonnell, “Work in Progress: PEER College Summer Camp”, Frontier in Education Conference, Oct. 19-22, Indianapolis, 2005.

- Justin Gregg and Tom Chen, “PEER: Enriching Secondary Engineering Education Through a College Summer Camp”, 2005 International Conference on Microelectronic Systems Education, Anaheim, CA, June 12 – 13, 2005.

- Vinil Varghese, Tom Chen, Peter Young, “On Stability of Active Clock Deskewing Systems Using a Control Theoretic Approach,” 2005 American Control Conference (ACC2005), Portland, OR, June 8-10, 2005.

- D. M. Sendek, D. Balhiser, J. Gregg, and T. Chen, “Post Silicon Power-Performance Optimization in VLSI Design”, Proceedings of 2005 SIAM Conference on Optimization, Stockholm, Sweden, May 16-19, 2005.

- J. Gregg and T. Chen, “Optimization of Individual Well Adaptive Body Biasing (IWABB) Using a Multiple Objective Evolutionary Algorithm,” International Symposium on Quality Electronic Design, San Jose, CA, March 21-23, 2005.

- V. Varghese, T. Chen and P. Young, “Systematic Analysis of Active Clock Deskewing Systems Using Control Theory”, Design and Test in Europe (DATE2005), Munich, Germany, March 7-11, 2005.

- A. Chandy and T. Chen, “Performance Driven Decoupling Capacitor Allocation Considering Data and Clock Interactions,” Design and Test in Europe (DATE2005), Munich, Germany, March 7-11, 2005.

- J. Pratt, M. Aydin, T. Chen, “RC Extraction of Interconnects at Sub-Wavelength Dimensions,” IASTED International Conference on Artificial Intelligence and Applications, Innsbruck, Austria, February 14-16, 2005.

- V. Varghese, T. Chen and P. Young, “Stability Analysis of Active Clock Deskewing Systems Using a Control Theoretic Approach,” 2005 Asia and South Pacific Design Automation Conference (ASP-DAC), Shanghai, China, January 18-21, 2005.

- A.M. Raza, G.W. Yuan, K.L. Lear, T. Chen, and C.K. Thangaraj, “Truly CMOS Compatible Waveguide Coupled Photodiode for On-Chip Optical Interconnects,” Conference on CMOS Compatible Photodetectors, IEEE LEOS, Puerto Rico, November 7-11, 2004.

- A.M. Raza, G.W. Yuan, K.L. Lear, T. Chen, and C.K. Thangaraj, “Waveguide Coupled CMOS Photodetector for On-Chip Optical Interconnects,” Conf. on Photonic Devices and Algorithms for Computing, Proc. of SPIE, SPIE Annual Meeting. Denver, CO. August 2-6, 2004.

- A. Andrew, A. O’Fallon, and T. Chen, “RUBASTEM: A Verification Method for Testing VHDL Behavioral Models,” 8th IEEE International Symposium on High Assurance Systems Engineering (HASE), Tampa, FL, March 25-26, 2004.

- T. Chen and J. Gregg, “A Low Cost Individual-Well Adaptive Body Bias (IWABB) Scheme for Leakage Power Reduction and Performance Enhancement In the Presence of Intra-Die Variations,” Design and Test in Europe (DATE2004), Paris, France, February, 2004.

- J. Gregg and T. Chen, “Post Silicon Power/Performance Optimization in the Presence of Process Variations Using Individual Well Adaptive Body Biasing (IWABB),” 5th International Symposium on Quality Electronic Design (ISQED), San Jose, CA, March 2004. (Nominated for best paper)

- M. Kulkami and T. Chen, “A Sensitivity Based Approach to Analyzing Signal Delay Uncertainty of Coupled Interconnects,” 5th International Symposium on Quality Electronic Design (ISQED), San Jose, CA, March 2004. (Nominated for best paper)

- G. Esch and T. Chen, “Design of CMOS Drivers with Less Sensitivity to Process, Voltage, and Temperature Variations,” 2nd IEEE Workshop on Electronic Design, Test and Applications (DELTA 2004), Perth, Australia, January 26-28, 2004.

- A. Andrew, A. O’Fallon, and T. Chen, “A Rule-Based Software Testing Method for VHDL Programs,” IFIP 2003 VLSI System-on-Chip (SoC) Conference, Darmstadt, Germany, December 1-3, 2003.

- T. Chen and A. Hajjar, “Analyzing Static Timing Behavior of Coupled Interconnects Using Quadratic Delay Change Characteristics,” 4th International Symposium on Quality Electronic Design (ISQED), San Jose, CA, March 24-26, 2003.

- G. Cho and T. Chen, “Comparative Assessment of Adaptive Body-Bias SOI Pass-Transistor Logic,” 4th International Symposium on Quality Electronic Design (ISQED), San Jose, CA, March 24-26, 2003.

- C. Deshpande and T. Chen, “Design of 0.18um CMOS Test Chip for Power Grid and I/O Characteristics Verification,” 2003 Asia and South Pacific Design Automation Conference (ASP-DAC), January 22-24, 2003.

- G. Cho and T. Chen, “On Single/Dual-Rail Mixed PTL/Static Circuits in Floating Body SOI and Bulk CMOS: A Comparative Assessment,” 16th International Conference on VLSI Design. New Delhi, India, January 4-8, 2003.

- G. Cho and T. Chen, “Application of Genetic Learning to Pass-Transistor Design and Optimization,” 4th Asia-Pacific Conference on Simulated Evolution and Learning, Singapore, November 18-22, 2002.

- G. Cho and T. Chen, “On the Impact of Technology Scaling On Mixed PTL/Static Circuits,” IEEE International Conference on Computer Design: VLSI in Computers and Processors (ICCD), Freiburg, Germany, September, 16-18, 2002.

- C. Deshpande and T. Chen, “Design of 0.18umm CMOS Test Chip for Package Models and I/O Characteristics Verification,” 45th IEEE Mid-West Symposium on Circuits and Systems, Tulsa, OK, August 4-7, 2002.

- Invited Paper, A. Hajjar and T. Chen, “A Dynamic Bayesian Based Stopping Criterion: A More Efficient Statistical Stopping Rule for Simulation-Based Behavioral Model Verification,” 2002 IEEE International Workshop on Microprocessor Test and Verification, Austin, TX, June 6-7, 2002.

- G. Cho and T. Chen, “On the Impact of Fanout Optimization and Redundant Buffer Removal for Mixed PTL Synthesis in UDSM CMOS Process,” IEEE/ACM 11th International Workshop on Logic and Synthesis, New Orleans, Louisiana, June 4-7, 2002.

- Invited Paper T. Chen, “High Performance Clocking for 10-20 GHz Microprocessors: Issues and Solutions,” IEEE Solid-Sate Circuit Council Workshop on Future 10-20 GHz Microprocessor Designs, in conjunction with International Solid-State Circuit Conference, San Francisco, CA, February 2002.

- G. Cho and T. Chen, “Mixed PTL/Static Logic Synthesis Using Genetic Algorithms for Low Power Applications,” IEEE International Symposium on Quality Electronic Design (ISQED), San Jose, CA, March, 2002.

- A. Hajjar and T. Chen, “Improving the Efficiency and Quality of Simulation Based Behavioral Model Verification Using Dynamic Bayesian Criteria”, IEEE International Symposium on Quality Electronic Design (ISQED), San Jose, CA, March, 2002.

- G. Cho and T. Chen, “Technology Mapping for Low Power SOC Using Genetic Algorithm,” IFIP International Conference on Very Large Scale Integration, Montpellier, France, December 3-5, 2001.

- J. Kim and T. Chen, “Real-time Video Objects Segmentation using a Highly Pipelined Microarchitecture,” International Conference Visualization, Imaging, and Image Processing (VIIP2001), Marbella, Spain, September 3-5, 2001.

- T. Chen, “On the Impact of On-Chip Inductance on Signal Nets Under the Influence of Power Grid Noise,” Design Automation and Test in Europe (DATE2001), Munich, Germany, March, 2001.

- A. Hajjar, T. Chen, I. Munn, A. von Mayrhauser, and M Bjorkman, “High Quality Behavioral Verification Using Statistical Criteria,” Design Automation and Test in Europe (DATE2001), Munich, Germany, March, 2001.

- T. Chen, “On the Impact of On-Chip Inductance When Transitioning From Al to Cu Based Technology,” International Symposium on Quality Electronic Design (ISQED). San Jose, CA, March, 2001.

- A. Hajjar, T. Chen, I. Munn, A. von Mayrhauser, and M. Bjorkman, “Stopping Criteria Comparison: Towards High Quality Behavioral Verification,” International Symposium on Quality Electronic Design (ISQED). San Jose, CA, March, 2001.

- J. Kim and T. Chen, “Low-Complexity Fusion of Intensity, Motion, Texture and Edge for Image Sequence Segmentation: A Neural Network Approach,” IEEE International Workshop on Neural Networks for Signal Processing, Sydney, Australia, December 2000.

- A. von Mayrhauser, T. Chen, J. Kok, C. Anderson, A. Reed, and A. Hajjar, “On Choosing Test Criteria for Behavioral Design Verification,” IEEE International High Level Validation and Test Workshop, Berkeley, CA, November 2000.

- A. Hajjar, T. Chen, and A. von Mayrhauser, “On Statiscal Behavior of Branch Coverage in Testing Behavioral VHDL Models,” IEEE International High Level Design Validation and Test Workshop, Berkeley, CA, November 2000.

- J. Kim and T. Chen, “A VLSI Architecture for Image Sequence Segmentation Using Edge Fusion,” International Workshop on Computer Architectures for Machine Perception, Padova, Italy, September 2000.

- J. Kim and T. Chen, “Segmentation of Image Sequences Using SOFM Networks,” 15th International Conference on Pattern Recognition, Barcelona, Spain, September 2000.

- J. Kim and T. Chen, “Neural Network Based Image Sequence Segmentation Using Multiple Features and Edge Fusion,” Advanced Concepts for Intelligent Vision Systems Symposium, Baden-Baden, Germany, July 2000.

- J. Kim and T. Chen, “An Integrated Approach to Image Sequence Segmentation,” IEEE Nordic Signal Processing Symposium, Vildmarkshotellet, Sweden, June 2000.

- T. Chen, M. Sahinoglu, A. von Mayrhauser, A. Hajjar, and C. Anderson, “Achieving the Quality of Verification for Behavioral Models with Minimum Effort,” IEEE International Symposium on Quality Electronic Design (ISQED), San Jose, CA, March 20-22, 2000.

- T. Chen and C. Alkan, “Measuring Routing Congestion for Multi-layer Global Routing,” 10th Great Lakes Symposium on VLSI, Chicago, Illinois, March 2-4, 2000.

- T. Chen, I. Munn, A. von Mayrhauser, A. Hajjar, “Efficient Verification of Behavioral Models Using the Sequential Sampling Technique,” 10th IFIP International Conference on VLSI (VLSI99), Lisboa, Portugal, December 1-4, 1999.

- T. Chen, M. Sahinoglu, A. von Mayrhauser, A. Hajjar, and C. Anderson, “How Much Testing is Enough? Applying Stopping Rules to Behavioral Model Testing,” 4th IEEE International Symposium on High Assurance System Engineering, Washington D.C., November, 17-19, 1999.

- J. Kim and T. Chen, “Integration of Multiple Features Using Back Propagation Neural Networks for Segmentation of Image Sequences,” International Conference on Image Science, Systems, and Technology, pp.65-71, Las Vegas, NV, June, 1999.

- M. Sahinoglu, A. von Mayrhauser, A. Hajjar, T. Chen, and C. Anderson, “On the Efficiency of a Compound Poisson Stopping Rule for Mixed Strategy Testing”, Proc. 1999 IEEE Aerospace Conference, Snowmass, Colorado, March 6-13, 1999.

- A. von Mayrhauser, A. Bai, T. Chen, A. Hajjar, C. Anderson, “Fast Antirandom (FAR) Test Generation,” 3rd IEEE High-Assurance Systems Engineering Symposium, Washington, DC. November 13-14, 1998.

- T. Chen, D. Anderson, P. Young “On Integrating Multi-Sensory Components In Virtual Environments,” 4th International Conference on Virtual Systems and MultiMedia, Gifu, Japan, November 18-20, 1998.

- A. Bai, T. Chen, A. von Mayrhauser, A. Hajjar, C. Anderson, “Fast Antirandom (FAR) Test Generation to Improve Code Coverage,” Quality Week’98, San Francisco, CA, May 27-30, 1998.

- T. Chen, P. Young, D. Anderson, “Development of a Stereoscopic Haptic Acoustic Real-Time Computer (SHARC),” Proceedings of SPIE, Vol. 3295, pp. 171-179, San Jose, CA, January 26-29 1998.

- P. Young, T. Chen, D. Anderson, “Legoworld: A Multisensory Environment for Virtual Prototyping,” Proceedings of SPIE, Vol. 3295, pp. 313-321, San Jose, CA, 26-29 January 1998.

- T. Chen, P. Young, D. Anderson, “Creating Virtual Environments Over the Internet, “Proceedings of SPIE, Vol. 3295, pp. 322-331, San Jose, CA, 26-29 Jan. 1998.

- V.Y. Kim, T. Chen, and M. Tegethoff, “ASIC Manufacturing Test Cost Prediction at Early Design Stage,” 1997 International Test Conference, Washington D.C. November 3-5, 1997.

- C. Chen and T. Chen, “Modified Rate-Distortion Function With Optimal Classification for Wavelet Coding,” 1997 International Conference on Image Processing, Santa Barbara, CA, October 26-29, 1997.

- A. Hajjar and T. Chen, “A New Real-Time Edge Linking Algorithm and Its VLSI Implementation,” International Conference on Computer Architectures for Machine Perception (CAMP’97), Boston, MA, October 20-22, 1997.

- V.Y. Kim and T. Chen, “IDDQ Testability Analysis Using Random Test Vectors,” 5th International Conference on VLSI and CAD, Seoul, Korea, October 13-15, 1997.

- C. Chen, J. Swanson, and T. Chen, “Applying High-Order Polynomial Type Global Constraints to Stereo Image Coding,” 1997 Picture Coding Symposium, Berlin, Germany, September 10-12, 1997.

- C. Chen and T. Chen, “Wavelet Coding By Using Interpolated Rate-Distortion Function and Classified VQ,” 1997 Picture Coding Symposium, Berlin, Germany, September 10-12, 1997.

- C. Chen, J. Swanson, and T. Chen, “Stereo Image Coding Using Object-Based Global Constraints,” International Workshop on Synthetic-Natural Hybrid Coding and Three Dimensional imaging, Rhodes, Greece, September 5-9, 1997.

- A. Hajjar and T. Chen, “A VLSI Architecture for Real-Time Edge Linking,” IX IFIP International Conference on VLSI, Gramado, Brazil, August 26-29, 1997.

- V.Y. Kim and T. Chen, “SRAM Yield Estimation in the Early Stage of the Design Cycle,” 1997 IEEE International Workshop on Memory Technology, Design and Testing, San Jose, CA, August 11-12, 1997.

- C. Anderson, A. von Mayrhauser, C.R. Gideon, T. Chen, and J. Kok, “Test Coverage Prediction of VHDL Models Using Neural Networks,” Annual Oregon Workshop on Software Metrics, May 11-13, 1997.

- V.Y. Kim and T. Chen, “Assessing SRAM Test Coverage for Sub-Micron CMOS Technologies,” 1997 VLSI Test Symposium, Monterey, CA, April 27-30, 1997.

- F. Alzahrani and T. Chen, “A Real-Time High Performance Edge Detector for Vision Applications,” 1997 Asia and South Pacific Design Automation Conference, (ASP-DAC’97) Makurahi Messe, Chiba, Japan, January 28-31, 1997

- Y.B. Kim and T. Chen, “A CMOS Delayed Locked Loop (DLL) for Reducing Clock Skew to under 500ps,” 1997 Asia and South Pacific Design Automation Conference, (ASP-DAC’97) Makurahi Messe, Chiba, Japan, January 28-31, 1997.

- C. Chen and T. Chen, “Hybrid Optimum Classification in Wavelet Transform Coding,” 1996 International Symposium on Multi-Technology Information Processing, Hsinchu, Taiwan, December 16-18, 1996.

- F. Alzahrani and T. Chen, “A Stand-Alone ASIC for Real-Time Edge-Detection,” 8th International Conference on Microelectronics, Egypt, December 16-18, 1996.

- Y.B. Kim and T. Chen, “A 0.8 m CMOS Delayed Loop for VLSI Systems with Sub-50ps Clock Skew,” 1996 IEEE Asia-Pacific Conference on Circuits and Systems, (APCCAS’96) Seoul, Korea, November 18-21, 1996.

- C. Chen and T. Chen, “Wavelet Coding With Region Classification Using Low-Complexity Prediction Model,” 13th Asilomar Conference on Signals, Systems, and Computers, Monterey, CA, November 3-6, 1996.

- V.Y. Kim, M. Tegethoff, and T. Chen, “Yield Estimation of ASIC Chips at Early Stage of the Design Cycle,” 1996 International Test Conference, Washington D.C., November 1996.

- C. Chen and T. Chen, “Wavelet Transform Coding with Linear Prediction and The Optimal Choice of Wavelet Basis Functions,” 1996 IEEE Nordic Signal Processing Symposium, Espoo, Finland, September 24-27, 1996.

- Y.B. Kim and T. Chen, “On System Level Performance of DRAM/Logic Merged Technology,” 1996 International Conference on Circuits/Systems, Computers and Communications, Seoul, Korea, July 15-17, 1996.

- Y.B. Kim and T. Chen, “Clock Skew on DRAM/Logic Merged Technology Based Systems,” 1996 International Symposium on Circuits and Systems (ISCAS), Atlanta, GA, May 12-15, 1996.

- Y.B. Kim and T. Chen, “Assessing DRAM/Logic Merged Technology,” 1996 International Symposium on Circuits and Systems (ISCAS), Atlanta, GA, May 12-15, 1996.

- C. Anderson, A. von Mayrhauser, and T. Chen, “Assessing Neural Networks as Guides for Testing Activities,” 3rd International Software Metrics Symposium, Berlin, Germany, March 1996.

- Y.B. Kim, V.Y. Kim, and T. Chen, “A 0.8 m CMOS Optical Clock Receiver Design,” The 7th International Conference on Microelectronics, Kuala Lumpur, Malaysia, December 18-21, 1995.

- M. Schaffer and T. Chen, “A VLSI Architecture for 2D Object Classification Based on Tree Matching,” Computer Architectures for Machine Perception (CAMP95), Como, Italy, September 18-20, 1995.

- M. Schaffer and T. Chen, “Object Parts Matching Using Hopeld Neural Networks,” Computer Architectures for Machine Perception (CAMP95), Como, Italy, September 18-20, 1995.

- C. Morganti and T. Chen, “Graceful Capacity Degradation for Ultra-Large Hierarchical Memory Structures,” 1995 IFIP VLSI Conference, Chiba, Japan, August 30-September 1, 1995.

- M. Tegethoff and T. Chen, “Board Test: Defects, Fault Coverage, Yield and Cost in Board Manufacturing,” 1994 International Test Conference, Washington D.C., October 1994.

- M. Tegethoff and T. Chen, “Manufacturing Test Simulator: A Concurrent Engineering Tool for Boards and MCMs,” 1994 International Test Conference, Washington D.C., October 1994.

- F. Alzahrani and T. Chen, “On-Chip TEC-QED ECC for Ultra-Large, Single-Chip Memory Systems,” 1994 IEEE International Conference on Computer Design: VLSI in Computers and Processors (ICCD), Cambridge, MA, October, 1994.

- G. Sunada, J. Jin, M. Berzins, and T. Chen, “COBRA: A 1.2 Million Transistor Expandable Column FFT Chip,” 1994 IEEE International Conference on Computer Design: VLSI in Computers and Processors (ICCD), Cambridge, MA, October, 1994.

- M. Tegethoff and T. Chen, “On Clustering of Defects and Yield of SMT Assemblies,” 1994 IEEE International Conference on Manufacturing Engineering, San Diego, CA, September 1994.

- G. Sunada and T. Chen, “A Novel DCT Implementation Using Bit-Serial Arithmetic,” 1994 IEEE Data Compression Conference, Snowbird, Utah, March, 1994.

- T. Chen and G. Sunada, “SIMSTGEN: A Simulation Based ATPG For Synchronous Sequential Circuits,” Annual Symposium of Technology Transfer Program, Colorado Advanced Software Institute, Denver, CO. 1992.

- T. Chen and G. Sunada, “An Ultra-Large Capacity Single-Chip Memory Architecture With Self-Testing and Self-Repairing,” IEEE International Conference on Computer Design: VLSI in Computers and Processors (ICCD), Boston MA, October 1992. (Recommended for Best Paper Award)

- T. Chen, D. Louderback, and G. Sunada, “Optimization of the Number of Levels of Hierarchy in Large-Scale Hierarchical Memory Systems,” International Symposium on Circuits and Systems (ISCAS). San Diego, CA, 1992.

- T. Chen and G. Sunada, “A Self-Testing and Self-Repairing Structure for Ultra-Large Capacity Memories,” 1992 International Test Conference, Baltimore, MD, September 20-24, 1992.

- T. Chen and L. Zhu, “A Fast 1024-Point FFT Architecture”, 1991 International Conference on Parallel Processing, St. Charles, Illinois, 1991.

Books and Book Chapters:

- “Application of Genetic Learning to Pass-Transistor Logic Design and Optimization” in Recent Advances in Simulated Evolution and Learning, Edited by Kay Chen Tan, Meng Hiot Lim, Xin Yao and Lipo Wang, World Scientific series on “Advances in Natural Computation,” 2003.

- Chapter 2, “Integrated Circuits,” in Microelectronics, Edited by Jerry C. Whitaker, CRC Press. 2000.

- “On the Promise of Neural Networks to Support Software Testing,” in Computational Intelligence in Software Engineering, Edited by W. Pedrycz and J.F. Peters, World Scientific Publisher, 1998.

- Chapter 45, “Integrated Circuits,” in The Electronics Handbook, Edited by J. C. Whitaker, CRC Press. 1997.

Walter Scott, Jr. College of Engineering

www.engr.colostate.edu

700 Meridian Ave

1301 Campus Delivery

Fort Collins, CO 80523-1301

(970) 491-3366

School of Biomedical Engineering

www.engr.colostate.edu/sbme

700 Meridian Ave

1376 Campus Delivery

Fort Collins, CO 80523-1376

(970) 491-7157

Walter Scott, Jr. College of Engineering

www.engr.colostate.edu

700 Meridian Ave

1301 Campus Delivery

Fort Collins, CO 80523-1301

(970) 491-3366

School of Biomedical Engineering

www.engr.colostate.edu/sbme

700 Meridian Ave

1376 Campus Delivery

Fort Collins, CO 80523-1376

(970) 491-7157